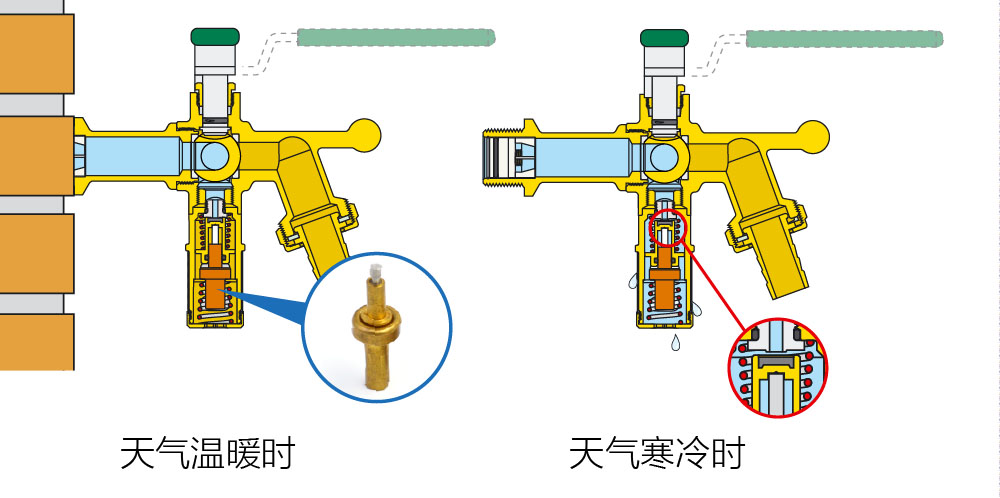

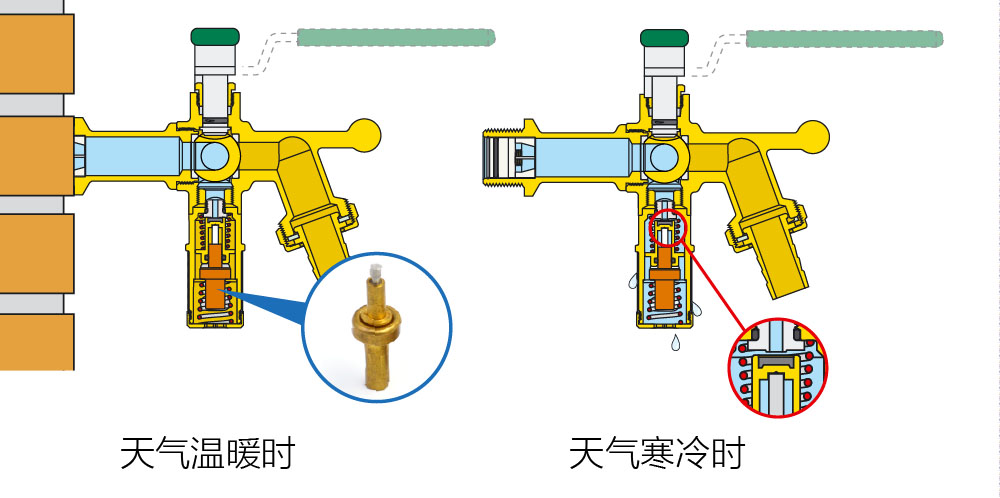

Environmental equipment control largely determines the quality of the test, and its process is accurate and complex. A more reasonable and efficient configuration solution will be found by analyzing the process. The whole control logic is stored and allocated by the central control unit.

According to different requirements, thermostatic element the central control unit will issue corresponding instructions. After acquisition of the receiving device, it will be further identified (amplification, frequency modulation, signal detection and correction), and then it will be transmitted to the comparative circuit to compare the storage characteristic curves in the signal and control unit. If the two are consistent, the system will determine that the executable identification link will adopt higher-level instructions. Through data transfer, in a certain range, the signal will be transmitted to the central control unit.

The data package is received by the protocol stack and transmitted to the upper layer. The macro definition related to the compiler word alignment corresponds to the destination address, source address and type field in the upstream respectively. When creating the process, the structure pointer of a network interface structure is passed in as a parameter.

If the data package is empty, the cycle ends, the next receiving process starts, the data in the data packet is obtained, and the type of the data packet is judged to only process the IP and ARP data packets, and the data packet is sent to the upper application function. There are three checks and balances in the process of packet reception. First, the method of data packet receiving bus is query mode, that is, the processor continuously reads data to the network card mutual trust buffer. If the data cannot be read temporarily, the controller will restart a clock reading sequence when the level flips. If the mechanism can successfully collect data, the redundant data will be registered through the input letter of the network card. Number contacts are handled by the upper class. The priority transpose level of the data packet receiving process using query mode must be lower than that of other processes in the system, otherwise it will block the decoding process running with lower priority. The above program has an improvement, that is, when the read data packet is empty, the receiving process calls the system function to delay itself for a period of time before starting the next reading process, so that it can not prevent the lower priority process from running. The disadvantage is that the receiving of the data packet can not respond in time. In fact, packet reception can be achieved by interruption, which is a better way. General network card chips have interrupt function, that is, when the network card receives a data packet, it can generate interrupt signal to tell the controller to receive a data packet. At this time, the controller starts a data packet reading sequence, which can effectively read non-empty data packets. So we can achieve a process of receiving data packets in this way: when no data packets are received, the process of receiving data packets is blocked in a semaphore.

When a data packet arrives, the network card chip generates an interrupt signal, and the processor enters the interrupt process and releases a semaphore. After the interruption exits, the data packet receiving process receives the semaphore, reads the data packet from the network card chip, and submits the data packet to the upper layer for processing. The second thing to note is the use of the htons (ethhdr – > type) function, which converts a half-word-long data from the network byte order to the byte order supported by our processor. Source code simulation debugging is implemented by one-step bifurcation, registers set breakpoints asynchronously, and interpret through heap before accessing locations. In the field of formatter architecture and computer communication, the admission mechanism for semituples and subtuples may be different. At present, there are two main storage mechanisms: big-endian and little-endian, i.e. the main end and the secondary end. For the total end mode, the high-bit bytes of a half-word or word data are locked in the low-address side of memory, and the low-bit bytes are placed in the high-address side of memory. For the Micro-end mode, the opposite is true.

Because the widely used ARM processor uses the secondary mode, and the received network byte data uses the total mode, so calling the function htons to realize the conversion between the primary and secondary end is to exchange the two bytes in order. After calling htons (ethhdr – > type), the value of ethhdr – > type is 0x0802 or 0x0808, etc.

Virtual terminal I2C can diagnose 32-bit operands through SPI serial communication debugging communication. RXD is used to receive data.

TXD sets up bus data transmission. The ASC II code input by lower computer is transmitted to PB port. The main loop process cooperates with advanced and complex interrupt program to realize network call of upper computer terminal, and loads executable files by using Usert keyboard separately. Execute the path to the compiled HEX file. Communication circuit can not push working instructions at the terminal. Simulations bypass hardware problems to determine whether software is wrong or not, encounter frequent obstacles to receiving and receiving independent feet, and then simulate actual operation to save debugging time.

The parameters of nodes in the loop can not correspond to each other one by one. Virtual instruments need to be connected. Logic analyzer opens debugging from compatible breakpoints, excludes the label of analog device DSP library from communication debugger, comprehensively uses digital, hybrid and frequency characteristic tools to detect potential difference point by point, and gradually becomes familiar with the characteristics of data packet stabilization by means of parameter configuration.

One step analysis leaves samples. By the equation ETU = FL (D * fs) (F = 542 for wide clock speed conversion factor, D for bit rate conversion factor FS for clock intersection frequency), the software basic path delay time is determined. The oscilloscope can visually observe the data I/O return to reset data waveform change, which is defined as initialization ATR (Aquire To Reset). Serial port resources account for a high proportion, resources are extremely limited, and general character. Under T0 protocol, data handover can be transplanted flexibly, satisfying SELEE command to select the storage area to be operated layer by layer, and returning UPDATE value referring to the internal file identification number of 6E2A meets the operation group indication condition. This file writing operation subclass is encapsulated as a function, and the main program as a sub-module of EEPROM extension and pseudo-code of test function. Software functions are interrupted by multi-row sockets, and display output is first activated for program testing. It mainly relies on the I/O stack structure to expand the function of reflection module to extract signals. Although 5.2V can also be used directly for USB board, the old external power supply is easy to be damaged. It is more stable to extract 7.3V across the switch board before the signal switching patch circuit uploads.

Before the boot Loader Flash guiding area pointer is lost, the program and control block matching will not react without following the key steps and adding the sensing signal. The thermoelectric indicator with the download port will always be bright, the long definition of electrical variables in the header file, and the variable initialization run once. The main work of P is to execute duplicates repeatedly, and then the environmental signal can be loaded on the pin after power-on. Careful package compilation results, grounding test write status, AVR direct programming code 72C8, generally 10 seconds later offline downrush, for FLASH solidification, should see port number operation response. The above process can explain many problems of poor control in signal analysis of environmental equipment, facilitate the capture and reproduction of various uncertain control problems, and has a perfect reference value for practical problem analysis.