Leakage current loss accounts for most of the energy consumption of the circuit and belongs to the dynamic process of real-time change. The traditional controller uses stack method to control the leakage current loss by controlling the input signal. It can not adapt to the dynamic change of leakage current and can not achieve the minimum loss control. For this reason, an electronic module of the controller considering the lowest leakage current loss is designed. The electronic module of the controller is designed by combining analog circuit with CPLD, and the overall structure of the design is given. The leakage current is detected by Hall sensor, and the actual leakage current is compared with the reference leakage current by comparator. The corresponding chopper driving signal is formed by CPLD and sent to the voltage controller. The on-off and on-off of the main switch device are controlled by the voltage controller to realize the control of the lowest leakage current loss. In the software design, a debugging software is designed, and the current minimum loss control program and the alternating chopper program are given. The experimental results show that the leakage current loss of the electronic module of the designed controller is very low and the operation efficiency is high. With the gradual development of electronic technology, related industries have entered the era of deep submicron and nanotechnology. Leakage current loss has become a key index to be considered in the process of electronic technology research [1?2]. In the field of electronic technology, the mechanism of leakage current is becoming more and more complex, and the impact of leakage current loss on power consumption is also growing. Therefore, it is of great significance to control the lowest leakage current loss, which is a key problem to be solved urgently. It has become a key research topic of relevant scholars and has attracted more and more attention [3?4]. At present, there are many studies on the Leakage Current Minimum Loss Controller, and some achievements have been achieved. In reference [5], a model-based leakage current minimum loss control method is proposed. This method controls the leakage current minimum loss according to the leakage current deviation constraint and voltage prediction method.

It can track the command signal effectively. However, this method is too sensitive to the change of parameters and reduces the predictive control to a certain extent. Dynamic performance. Literature [6] proposes a stack-based leakage current minimum loss controller, which connects several transistors together. If one or more transistors are closed, the leakage current will be significantly lower than that of a single transistor. According to the stack principle, the clock-gated signal is regarded as a control signal of dormant mode. If the circuit is in standby state, the circuit will form a set input vector, which will make as many transistors as possible in the stack state, so that the leakage current can be controlled in the minimum loss. However, the implementation process of this method is complex and it is not suitable for practical application.

Literature [7] designs a leakage current minimum loss controller based on variable threshold, which controls leakage current by changing substrate bias voltage. When the circuit is in a dormant state, a negative bias voltage is added to the substrate to increase the threshold voltage and cut off the leakage current. When the circuit is in operation, a relatively low positive bias voltage is added to the substrate to improve the circuit efficiency. However, the method takes too long and the efficiency is very low. Literature [8] designs a leakage current minimum loss controller based on multi-threshold, which introduces a high threshold NMOS transistor and regards the input signal as its control signal. In order to reduce the influence of NMOS transistor on circuit performance, the on-resistance of NMOS transistor is minimized. With the increase of the on-resistance of NMOS transistor, its width decreases and leakage current loss decreases, but with the decrease of the width of NMOS transistor, its performance decreases. Aiming at the drawbacks of the above methods, a controller electronic module considering the lowest leakage current loss is designed. The electronic module of the controller is designed by combining analog circuit with CPLD. The overall structure of the design is given, and the hardware structures are analyzed in detail. In the software design, a debugging software is designed, and the current minimum loss control program and the alternating chopper program are given.

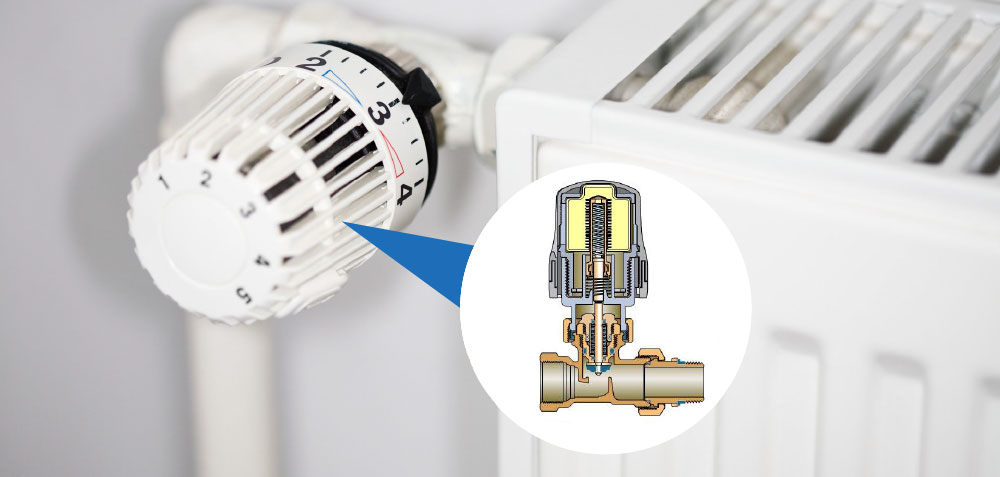

The experimental results show that the leakage current loss of the electronic module of the designed controller is very low and the operation efficiency is high. By combining analog circuit with CPLD, the electronic module of the Leakage Current Minimum Loss Controller is designed. This method not only has fast response, strong tracking ability, high real-time performance, but also is not easily disturbed by environmental factors and more reliable control. The overall design of the electronic module of the controller is shown in Figure 1. Fig. 1 shows that the leakage current is detected by Hall sensor, and the actual leakage current detected is compared with the reference leakage current by a comparator. If the actual leakage current does not exceed the reference leakage current, the low-level signal is output; otherwise, the output signal of the comparator is transmitted to CPLD; and the code of the leakage current minimum loss control program is transmitted from PC.

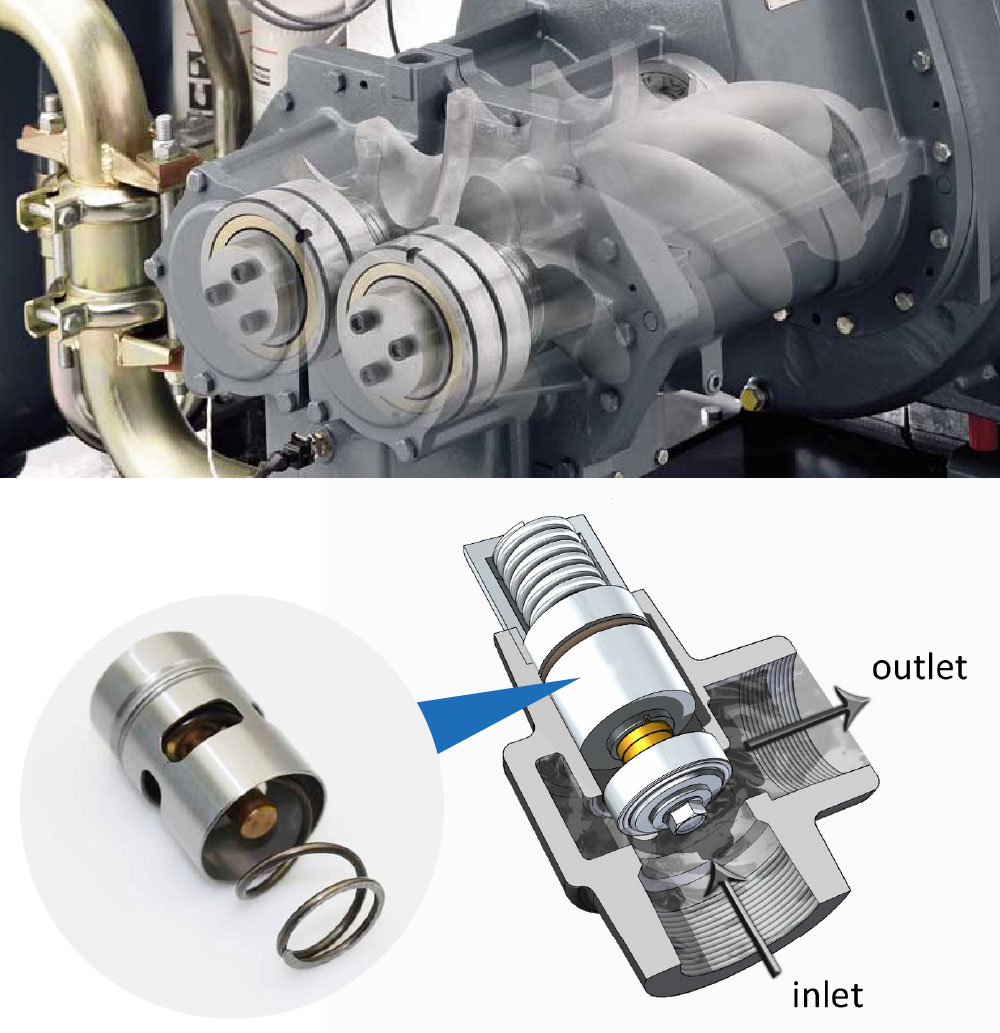

The machine is downloaded to the CPLD chip, and the corresponding chopper driving signal is formed by the CPLD and sent to the voltage controller, which controls the turn-on and turn-off of the main switching device to achieve the control of the lowest leakage current loss. In the controller considering the lowest loss of leakage current, the leakage current must be detected first. Figure 2 is a part of the circuit for leakage current detection. The magnetic field balanced Hall current sensor LT108? S7 is selected to detect leakage current. It not only has high detection accuracy, but also has fast response and strong anti-interference performance. It can realize electrical isolation detection. The electronic module of the controller needs only one sensor. The conversion rate of LT108? 57 is 1:2 000, that is to say, the leakage current measured is 2,000 times of the output current.

The leakage current measured can be obtained indirectly through the output current. I? FBC pin output. The comparator compares the actual leakage current detected with the reference leakage current. If the actual leakage current does not exceed the reference leakage current, the comparator will output a low-level signal; otherwise, the comparator will send the output signal to the CPLD. The comparator chooses LM393H dual voltage comparator, and its circuit diagram is shown in Figure 3. LM393H power supply has a wide voltage range and low energy consumption. Its output can be compatible with TTL, MOS, CMOS, etc. The leakage current signal detected by leakage current, I? FBA / I? FBB / I? FBC. The reference leakage current is sampled by RP1 to be a voltage signal by adding the sampling resistance to the in-phase input of LM393H, and then entered into LM393H by the inverted input. RP1 is a rheostat whose terminal voltage can be adjusted in the range of 0-2.75 V to change the reference current. If I? FBA / I? FBB / I? FBC exceeds the reference leakage current, LM393H will output a high level signal; conversely, it will output a low level signal.

After the comparator transmits the output signal to the CPLD, the CPLD will output the corresponding chopper driving signal to the voltage controller. The CPLD chip and the main switch driver output circuit are shown in Fig. 4. The code of leakage current minimum loss control program is downloaded from PC to CPLD chip. The model of controller electronic module is EPM1270T144C5 CPLD chip. It is manufactured by ALTERA Company. It chooses a new CPLD architecture, which not only has low cost, but also consumes only the original [110,] but also has high performance. The comparison signals of actual leakage current and reference leakage current are transmitted to CPLD through AOC/BOC/COC pins, and the output chopper signal of CPLD drives the voltage controller to realize the minimum loss control of leakage current. A large number of studies have shown that leakage current loss can be reduced by reducing voltage. When the actual leakage current is larger than the reference leakage current, the leakage current loss will be significantly reduced by reducing the voltage. However, when the actual leakage current is lower than the reference leakage current, the normal voltage is still used. Therefore, it is necessary to design a voltage controller to provide different voltages for different situations in order to achieve the purpose of leakage current minimum loss control. The main circuit of the voltage controller is shown in Fig. 5. In Fig.

5, the asymmetric half-bridge circuit is used to control each two main switches separately. The voltage controller can provide the required energy to achieve the purpose of the switch. The chopper signal obtained by CPLD is input by PA? UP / PB? UP / PC? UP and PA? DOWN / PB? DOWN / PC? DOWN to control the turn-on and turn-off of the main switch device. In order to facilitate the real-time acquisition of leakage current signal, a debugging software is designed. The interface of the debugging software is shown in Figure 6. The functions of the software include real-time tracking, parameter setting and so on. In software design, the design of alternating chopper is particularly important. Detailed design scheme is as follows: setting a main switch selection signal cho, when the OA is in the rising edge state, CHO flips, thermostatic element Cho is 1, AH1 disconnects, Cho is 0, VT2 disconnects. In order to verify the validity of the electronic module of the controller designed in this paper considering the lowest leakage current loss, relevant experimental analysis is needed. In the experiment, permanent magnet synchronous motor (PMSM) is taken as the research object, and stack controller is taken as the comparative analysis.

The detailed parameters of PMSM studied are shown in Table 1. The physical diagram of the experimental platform is shown in Figure 7. Under the above experimental platform, the leakage current loss is controlled by the proposed controller and stack controller respectively. The results are shown in Table 2. The analysis table 2 shows that under the same conditions, the loss of leakage current control by the controller in this paper is lower than that of the stack controller, and has been lower than that of the stack controller all the time. It shows that the control performance of the controller in this paper is higher, which verifies the reliability and effectiveness of the controller in this paper. To further verify the effectiveness of the proposed controller, the running time of the two controllers is compared, and the results are shown in Figure 8. Analysis of Figure 8 shows that compared with the stack controller, the time required to adopt the controller in this paper is significantly reduced, which shows that the controller in this paper not only has high control performance, but also has high operational efficiency. This paper designs an electronic module of the controller considering the lowest leakage current loss. The electronic module of the controller is designed by combining analog circuit with CPLD. The leakage current is detected by Hall sensor. The actual leakage current detected is compared with the reference leakage current by comparator and CPL. D forms the corresponding chopper driving signal and sends it to the voltage controller, which controls the turn-on and turn-off of the main switching device to realize the control of the lowest leakage current loss. A debugging software is designed, and the current minimum loss control program and the alternating chopper program are given. The experimental results show that the leakage current loss of the electronic module of the designed controller is very low and the operation efficiency is high.