DDR SDRAM uses double data rate structure. With its advantages of large capacity, high data transmission rate and low cost, it is increasingly used in high-speed data acquisition systems. The function of DDR controller is designed and implemented by using Cyclone FPGA chip of Altera Company.

The design idea is described, which has certain practical value. With the rapid development of electronic technology, the demand for DDR (full name DDR SDRAM) [2] is becoming more and more urgent. DDR (Double Data Rate Synchronous Dynamic Random Access Memory) is designed with a 2.5V working voltage, and allows data access at the rising and falling edges of the clock. The overall speed of DDR is twice the same frequency, and it also shows better performance in terms of capacity. Therefore, in many important systems with high requirements for data volume and bandwidth, DDR has become a powerful and extensible high-end memory widely used.

Based on this, in order to give full play to the advantages of DDR’s capacity and speed, this research mainly aims at the characteristics of DDR’s reading and writing, and develops and implements a DDR controller based on FPGA reading and writing. DDR SDRAM is composed of several basic single-tube DRAM units. The main function of the memory controller is to control the read and write of DDR3 SDRAM. After the initialization of the memory chip, the DDR memory is ready. DRAM uses the charge on the gate capacitor of the MOS transistor to store information. Whether a unit stores 0 or 1 depends on whether the capacitor has charge. Charge represents 1, and no charge represents 0. However, over time, due to grid leakage, capacitors representing 1 will discharge and capacitors representing 0 will absorb charges, which will result in data loss. After DDR SDRAM is powered on, its internal and stored values are unknown. Initialization operation must be carried out to make it work normally. Initialization process is: after the system is powered on, keep CKE low level, wait for the stability of power supply voltage and clock. When the power supply voltage and clock voltage are stable, the reset signal is kept valid.

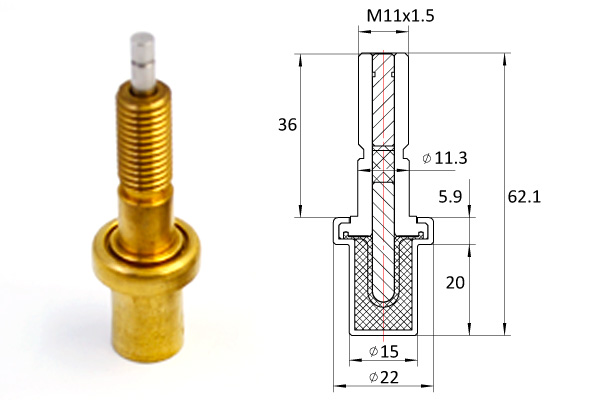

After completing the initialization step, the DDR3 storage will enter the ready state, waiting for the controller’s access command, and can perform normal work, and according to the command issued by the controller to perform the corresponding operation. The working form of DDR3 is the process of transformation of different states, thermostatic element that is, free transformation between different states through the control of state machine. The main function of DDR SDRAM controller is to complete the initialization of DDR SDRAM, convert the complex read-write sequence of DDR SDRAM into user’s simple read-write sequence, and convert the double clock of DDR SDRAM interface into user’s single clock along data, so that users can customize and control DDR SDRAM as they operate ordinary RAM.

Periodic refresh commands to maintain data in DDR SDRAM without user intervention [4]. The working principle of the design and implementation is shown in Figure 1. As shown in Figure 1, the processing function of the main control module is to initialize the memory, then accept and decode user information to generate instructions such as read, write or refresh. The logic design is provided by the state machine for overall management and implementation. The state transition of DDR is shown in Figure 2. Figure 2 shows that after DDR SDRAM is powered on, the initialization process must be started according to the prescribed procedure.

In the initialization process, attention should be paid to whether the values of the common mode register and the extended module register are correct. Among them, general registers are mainly used to set the working mode of DDR SDRAM, including burst length, burst type and mode [5]. When the initialization process is finished, it will be imported into the normal working state, at which time the memory can be read, written and refreshed. Before the read-write operation occurs, the ACTIVE command needs to be executed. The address triggered with the ACTIVE command is used to select the burst start column unit.

There is also a pre-charging operation before activation, and only after the pre-charging operation is closed, DDR SDRAM can set read and write operations on new areas or rows. DDR controllers need to use automatic refresh commands to keep their internal data from being lost, but they must be executed when all zones are idle. Write operation is to write data to DDR SDRAM by FPGA. It only needs to issue corresponding working instructions according to the working requirements of DDR SDRAM. The frequency of DDR can be described and expressed in two ways: working frequency and equivalent frequency. Specifically, the working frequency is the actual working frequency of memory particles, but because DDR memory can transmit data along the rising and falling edges of the pulse, the equivalent frequency of data transmission is twice the working frequency. Based on this, the technical classification of DDR can be obtained. The classification results are shown in Table 1. Nowadays, the series of FPGA chips in Xilinx system have already occupied a super market share, and their development prospects are considerable. All kinds of situations make ISE develop into the preferred tool software of FPGA which is widely used so far. ISE is a set of tools that can efficiently implement EDA design, and can complement the skills and advantages of some third-party software, so that the software functions of ISE are becoming more and more perfect, at the same time, it is more suitable for today’s development needs. ISE is characterized by friendly interface and simple operation. The main functions of ISE include design input, synthesis, simulation, implementation and download. Its workflow does not require any software support. DDR2 controller is composed of four modules: clock module, control module, data link module and user interface module. In this paper, the implementation functions of each module are explained as follows. The clock module is composed of Xilinx’s DCM core aggregation design and implementation. It is mainly used to receive the external clock of the FPGA, and then generates user interface clock, data link module clock, control module clock and DDR2 clock through frequency division and frequency doubling. Moreover, another customized function of the module is to reset the whole module globally with reset signal. [BT5]4.2 control module is the center of the controller. The control module is mainly used to perform the initialization and command operation of DDR 2. Therefore, the basic design of the control module is mainly composed of initialization and command control. The detailed analysis is as follows. Initialization. After DDR2 is powered on, the clock-enabled signal CKE is set up at a stable time of 20 mu s. After 400 ns, the first pre-charging is carried out.

Then the configuration process is opened for the external registers and mode registers. Then the second pre-charging and two refreshes are executed to determine whether the DLL is locked correctly, OCD is configured, and finally the initialization is completed. 。 If the initialization is over, elevating the signal initial_done indicates that the user can perform further operations on DDR2 at this time. Command control. The command control part is mainly used to generate control signals and delay in each operation after DDR2 initialization, and to analyze user commands to set automatic refresh, read, write, pre-charge and other operations for DDR2. When the user writes the read-write command, the state machine can decide whether the initialization is completed, the row activation, the column addressing, the pre-charging, the automatic refresh, the publication of the read-write command and so on. DDR2 is a high-speed chip that can perform data sampling on both the upper and lower edges of the clock. Therefore, the timing of data link module will be strictly required. In order to achieve this design goal, the special primitive modules IDDR and ODDR of Xilinx SPARAN6 are used to process the data. In data link module, read data link and write data link are independent of each other, which makes it easier for users to obtain clear control over data. As a key module directly connected with users, the completeness of user interface module will directly affect the difficulty of user control over IP core.

In order to make it easy for users to apply the IP core of the controller to the project, the whole module includes READ FIFO, WRITE FIFO, COMMAND FIFO, command sub-module, user data link sub-module and user control sub-module. Among them, READ FIFO, WRITE FIFO and COMMAND FIFO enable users to fully control the continuous input and output of commands and data. The command sub-module can translate the command input by the user.

The user only needs to send the read or write command, the first address of the command to be operated and the total number of data read/write. The command sub-module can send command control to the user control sub-module according to the situation. User control sub-module controls COMMAND FIFO, WRITE FIFO and READ FIFO in the form of state machine. It provides functional control for the main control module and data link module connected with user interface module, and sends out operation instructions such as reading/writing to DDR2. DDR SDRAM operates under the control of a pair of differential clocks. The instruction is set to trigger the rising edge of each clock.

Along with the data transmission, a DQS (two-way data selective signal) is also included. The receiver can receive some customized data through this selective signal. The DQS selected signal has some connection with the data, and its function is equivalent to a clock working independently. DQS, as an optional signal, is constructed by DDR SDRAM during the reading cycle. When reading, the DDR controller captures data by directly acquiring the clock. After acquiring the clock trigger signal, the data will be displayed on the data bus after triggering the read-write delay. In the process of writing cycle, the generation of DQS (bidirectional data selective signal) is designed and implemented by DDR controller. During the writing cycle, the data selector signal will align with the data in the center. The timing of read/write operations is shown in Figure 3. After the hardware design and Simulation of the system are established, the compiled files can be downloaded to the hardware of the system, and the read signals of the DDR SDRAM controller can be collected and displayed in real time. You can use a single step to execute the program and then go to the memory window to observe the current content of the DDR SDRAM address space [7]. The display effect is shown in Figure 4. A total of 751 4-input LUTs are used in the design of DDR controller, which is only 2% of the total LUT resources. In addition, three DCM are used in the design. DDR controller is realized in Xilinx ISE programming environment, and real-time observation is made with chipscope. When debugging on board, the final clock is 100 MHz. The test shows that the data transmission and acquisition are accurate. The DDR controller works practically, stably and reliably.

It occupies less logic resources. It not only shows high portability, but also has a simple and convenient user interface.

That is to say, it is more convenient and fast to use, and it can control other types of DDR SDRAM chip without complicated modification. Therefore, it can significantly improve the storage capacity of signal processing board, and can be used in high-speed signal processing system with high efficiency and quality.